前言

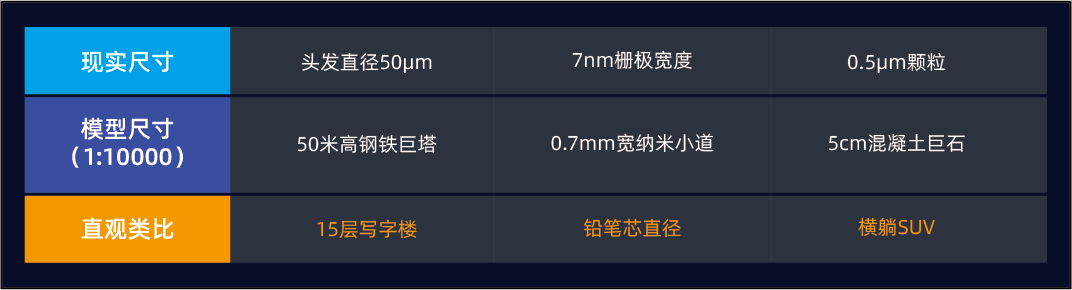

在半导体制造的纳米级战场上,一场由0.5µm颗粒引发的"尺寸暴动"正在改写产业规则。当我们将现实世界按1:10000的比例缩小,一根直径50µm的头发会化作50米高的钢铁巨塔,而7nm的晶体管栅极则缩成0.7mm宽的羊肠小道。这场微观世界的"巨人入侵",正是中国7nm芯片制造面临的核心挑战。

一、尺寸暴动:1:10000比例下的灾难推演

(一)现实与模型的尺寸映射

这种尺寸差异相当于让大象穿行在毛细血管中——当50米高的巨塔矗立在纳米城市中央,0.7mm宽的通道根本无法容纳其存在。半导体的5nm蚀刻设备虽能实现2000层3D NAND选择性蚀刻,但在0.5µm颗粒面前仍显力不从心。

(二)颗粒污染的三重灾难

完全遮蔽效应:5cm巨石精准覆盖0.7mm通道,导致晶体管彻底失效。麒麟9010芯片采用的FinFET结构,其沟道长度仅0.3µm,任何颗粒入侵都会造成灾难性后果。

短路桥接效应:巨石横跨两条纳米通道,造成50%概率的短路。半导体的CN119993908A专利虽将非晶硅沉积缺陷密度降至10⁶/cm²,但面对颗粒污染仍需依赖电子束检测。

线宽漂移效应:0.7mm通道允许的误差仅±0.07mm,而5cm巨石的挤压会使线电阻激增300%。这种效应在TSMC 7nm工艺中会导致芯片功耗提升25%。

二、经济地震:微观灾难的宏观代价

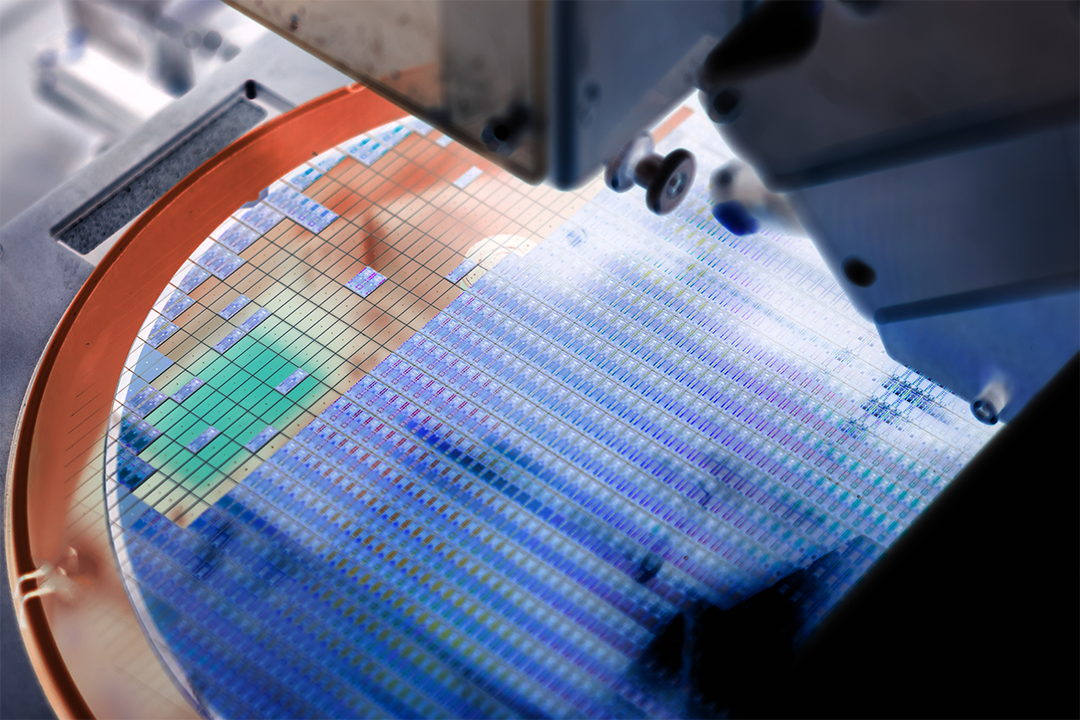

(一)晶圆级的财富毁灭

每片7nm晶圆包含500颗芯片,单颗价值约15000美元。当0.5µm颗粒引发故障时,相当于:

压毁500条纳米通道,直接损失750万美元,良率下降1个百分点即损失15万美元,部分企业的28nm DUV光刻机虽已量产,但在7nm制程中,单个颗粒造成的损失仍相当于压扁5辆劳斯莱斯幻影。

(二)检测盲区的幽灵威胁

现有光学检测技术对0.5µm颗粒的捕获效率不足50%,如同:

在50米高空无法发现5cm障碍物,需依赖价值200万元的电子束检测设备,检测成本占芯片制造成本的12%,这种困境在7nm工艺中表现为:每万片晶圆需额外投入300万美元进行缺陷分析。

(三)清洗工艺的极限挑战

传统湿法清洗在0.7mm通道边缘留下0.21mm清洁死角,相当于:

在50米巨塔周围留下42米宽的卫生盲区,需采用的兆声波清洗技术,清洗成本提升至每片晶圆1500美元,这种挑战在Intel 7nm工艺中导致清洗工序耗时增加40%。

三、技术突围:中国方案的尺寸革命

(一)材料纯度的尺寸突破

中国工厂生产的6N级超高纯金属靶材(纯度99.9999%)已占据全球40%市场份额,其精度达到:

杂质含量<1克/吨,支撑3nm芯片制造,使ASML工程师重新校准检测设备,这种材料革命相当于为纳米城市铺设绝对平整的"地基",从源头上减少颗粒生成。

(二)设备创新的尺寸压缩

中国企业深耕设备创新,研发EUV替代技术样机,通过:

碳纳米管冷却镜片,非球面镜组设计设备体积压缩至ASML的1/3这种创新相当于在纳米世界中建造更精密的"交通指挥系统",将颗粒污染风险降低60%。

(三)工艺优化的尺寸控制

中国半导体的Prismo UHC设备与PECVD设备形成技术闭环,实现:

非晶硅沉积缺陷密度从10⁹/cm²降至10⁶/cm²先进封装基板良率提升20%,7nm工艺步骤从1000道缩减至800道,这种精度提升相当于将城市道路的平整度标准从米级提升至微米级。

四、未来之战:尺寸博弈的终极推演

当工艺节点推进至2nm时,栅极宽度将缩至0.2mm,此时0.5µm颗粒的相对高度将膨胀至25倍。这相当于:

用50米巨石碾压0.2米宽的乡间小道,颗粒污染风险提升10倍,清洗难度呈指数级增长,面对这种挑战,中国通过"以成熟养先进"策略,在28nm制程领域占据全球33%份额,为技术突围积累资金。国家大基金三期3440亿资金中,50亿专项支持攻克EUV技术,这种战略投入相当于在纳米世界中建造"防洪大坝"。

尾言

在这场纳米级的"巨人战争"中,中国半导体产业正通过材料、设备、工艺的全链条创新构建防御体系。"当我们在28nm领域做到极致,那些被卡脖子的高端技术,反而会成为我们重新定义行业规则的突破口。"这场静默的技术革命,正在将0.5µm的"尺寸暴动"转化为中国芯片突围的阶梯。当50米高的钢铁巨塔最终融入纳米城市的天际线,中国芯片制造的黄金时代或将就此开启。