前言:良率战争进入“分子级”

在2nm节点的晶体管中,栅极长度仅容纳10个硅原子。若将晶体管放大至足球场大小,一粒0.1μm的颗粒便如卡在球门区的一辆汽车——它不会仅堵塞通道,而是直接改写器件电学特性:漏电流激增10倍,阈值电压漂移50mV,SRAM单元失效概率飙升1000倍。

半导体厂的每日算术题:“每增加1颗50nm颗粒,良率损失多少?”答案从0.01%到3%不等,取决于颗粒落在哪一工艺层、哪一道工序、哪一类器件上。

核心矛盾:当制程逼近原子级,超微颗粒从“偶然缺陷”升级为“系统性风险”,良率控制从“工艺优化”演变为“分子级战争”,而封装环节作为芯片制造的“最后一公里”,其颗粒污染风险正成为决定良率和可靠性的关键变量。

一、工序拆解:400道工序的长链,哪里最易被“灰”击穿?

1. 衬底制备(Ingot → Wafer)

单晶拉制:1450℃熔融硅中,若混入10¹⁰ atoms/cm³的碳或氧,后续热处理将析出SiC或SiO₂颗粒,成为位错源。

线切割+研磨:金刚石线掉粉、SiC研磨液残留,在表面留下20-80nm划痕;划痕底部应力集中,外延生长时易产生堆垛层错,导致单片晶圆报废率上升5%。

2. 前道工艺(FEOL)

热氧化/沉积:炉管石英件剥落的SiO₂微粒若落在栅极区,等同于在氧化层中埋入“微型MOS”,栅压升高时直接短路。

光刻:掩膜版上的50nm灰尘,经4×缩小曝光后仍占12.5nm,足以截断一根16nm金属线,导致单芯片功能失效。

干法刻蚀:腔体聚合物剥落后,CFₓ颗粒被高能离子轰击嵌入沟槽侧壁,形成侧壁漏电通道,良率损失呈指数级上升。

离子注入:光刻胶残渣未清除时,碳氢颗粒在1000℃退火中碳化,形成“黑硅”尖锥,击穿电压骤降30%,整批晶圆需返工。

3. 后道工艺(BEOL)

CMP铜互连:研磨液中Al₂O₃或SiO₂磨粒残留于铜/低k界面,RC延迟增加5%-8%,导致芯片时序失效,测试环节淘汰率上升15%。

4. 封装工艺(Packaging)

从“晶圆级”到“系统级”的颗粒风险放大封装环节涉及晶圆切割、芯片贴装、引线键合、塑封等多道工序,其颗粒污染来源更复杂、影响更隐蔽,且一旦发生失效,返修成本远高于前道工序。

(1)晶圆切割(Die Sawing)

颗粒来源:金刚石刀片磨损产生的微粉(1-10μm)、冷却液残留、晶圆背面粘片胶碎屑。

失效模式:切割道颗粒嵌入芯片边缘,导致后续封装时应力集中,芯片开裂风险提升30%;大颗粒(>5μm)划伤芯片表面钝化层,引发漏电或腐蚀,良率损失达5%-8%。

(2)芯片贴装(Die Bond)

颗粒来源:贴片胶中的填料颗粒(如Ag微粉)、基板表面氧化层剥落、环境灰尘。

失效模式:5μm以上颗粒导致芯片与基板间出现“虚贴”,高温高湿(THB)测试后剪切力下降40%,失效概率呈指数级上升;纳米级颗粒(<100nm)嵌入贴片胶界面,形成局部应力集中点,导致芯片在热循环测试中开裂。

(3)引线键合(Wire Bond)

颗粒来源:键合丝表面氧化层、超声焊接头磨损碎屑、环境有机污染物。

失效模式:3μm以上颗粒导致金球与铝垫接触不良,键合强度下降50%,早期失效率增加20%;亚微米颗粒(0.1-1μm)引发键合界面电迁移,电阻漂移超过20%,长期可靠性失效。

(4)塑封(Molding)

颗粒来源:环氧模塑料(EMC)中的填料团聚、模具表面脱模剂残留、空气中的纤维碎屑。

失效模式:50μm以上颗粒导致塑封体内部空洞,芯片在热冲击测试中分层风险提升5倍;纳米级颗粒(<100nm)作为水汽渗透通道,加速芯片腐蚀,失效率在HAST(高加速温湿度应力测试)中激增10倍。

二、痛点分级:从“看得见的刮痕”到“看不见的陷阱”

图表分析如下所示:

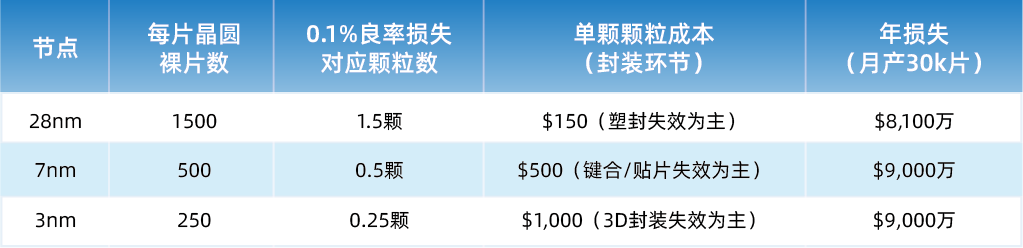

三、经济损失模型:把颗粒换算成美元

图表分析如下所示:

隐含逻辑:先进制程中,封装环节单颗颗粒成本虽低于前道工序,但其失效模式更复杂(如热机械失效、电化学迁移),返修成本占芯片总成本的30%-50%;3nm产线若因封装颗粒污染导致良率爬坡延迟3个月,直接损失超15亿美元(含研发分摊成本)。

四、系统性风险:当颗粒成为“放大器”

工艺窗口坍缩:EUV光刻焦深仅100nm,30nm颗粒即可使图形失焦;而封装环节中,5μm颗粒即可导致3D堆叠芯片层间对准偏差>1μm,整颗芯片报废;SAQP流程中,颗粒导致四次刻蚀图形错位累积;而在封装TSV刻蚀中,纳米颗粒引发侧壁粗糙度超标,电阻增加20%。

可靠性雪崩:Cu/low-k结构中的20nm颗粒成为电迁移空洞成核点;而在封装互连中,100nm颗粒即可引发微孔填充不全,导致热循环失效概率提升10倍;

塑封体中的纳米级水汽通道(由<50nm颗粒引发)使芯片在HAST测试中失效时间从168小时缩短至24小时。

研发成本失控:台积电3nm产线投资超200亿美元,若因封装颗粒污染导致良率爬坡延迟6个月,直接损失超30亿美元;英特尔3D封装技术(Foveros)因颗粒污染导致层间空洞问题,研发周期延长18个月,错失市场窗口期。

尾言:颗粒不再是“缺陷”,而是“成本放大器”

在2nm之后,晶体管已无“多余空间”容纳外来原子:

1.物理极限:栅氧厚度≤3个原子层,任何颗粒均等同于工艺灾难;

2.经济极限:一座3nm晶圆厂投资200亿美元,良率波动1%即可决定盈亏平衡;

3.封装新挑战:3D封装、Chiplet等新技术将颗粒风险从“二维平面”扩展至“三维空间”,单颗纳米颗粒即可引发系统级失效。

4.终极挑战:当芯片制造进入“埃米时代”,超微颗粒从“偶然缺陷”升级为“系统性成本放大器”。谁能在400道工序(含封装)中将50nm以下未知颗粒降至统计学零,谁才有资格定义下一代摩尔定律。