前言

在半导体制造的微观世界里,一粒直径≤0.5μm的超微颗粒,正成为7nm及以下先进制程的“隐形杀手”。当光刻胶中的纳米级尘埃附着在晶圆表面,或蚀刻腔体内的金属污染物未被彻底清除,这些肉眼不可见的颗粒便会引发连锁反应——在7nm制程中,一个直径0.3μm的缺陷可能导致超过10万颗晶体管失效,直接摧毁一片价值数万美元的晶圆。这场由“一粒灰”引发的灾难,正将全球半导体制造推向物理极限的悬崖边缘。

量子隧穿效应:电子的“越狱”狂欢

当晶体管栅极长度缩小至7nm,量子隧穿效应从理论预言变为现实噩梦。传统硅基晶体管中,栅极氧化层厚度已逼近1.2nm,仅相当于3-4个硅原子层。此时,电子不再遵循经典物理的“轨道”运动,而是以概率波的形式存在,导致约15%的电子会直接穿透绝缘层,形成漏电流。这种“电子越狱”现象在7nm制程中尤为严重:台积电N7工艺的实测数据显示,单个晶体管的静态功耗较10nm制程激增40%,而漏电流导致的良率损失高达12%。

更致命的是,量子隧穿与超微颗粒形成恶性循环。当0.5μm颗粒附着在栅极表面时,会局部改变氧化层厚度,使隧穿概率呈指数级上升。三星7nm EUV产线的失效分析报告显示,在含有颗粒污染的晶圆上,晶体管的亚阈值摆幅(SS值)恶化至85mV/dec,远超设计指标的65mV/dec,直接导致开关特性失效。这种微观层面的失控,使得每片晶圆需要额外增加3道清洗工序,却仍无法完全遏制良率下滑。

光刻极限:EUV光刻机的“纳米级颤抖”

极紫外光刻(EUV)技术虽被视为7nm制程的救世主,但其本身却对超微颗粒极度敏感。EUV光源通过锡滴靶材的激光轰击产生13.5nm波长的极紫外光,但这一过程会伴随大量纳米级锡颗粒的喷发。ASML的TWINSCAN NXE:3600D光刻机虽配备双重防护系统,仍无法完全阻止0.1μm以上的颗粒进入光路。这些颗粒在反射镜表面形成微小凸起,导致光刻图案产生1-2nm的偏移——在7nm制程中,这相当于允许误差的200%。

台积电的量产数据显示,EUV光刻环节的颗粒污染导致晶圆边缘区域的线宽均匀性(CDU)恶化至4.2nm,远超中心区域的2.8nm。为弥补这一缺陷,工程师不得不将曝光剂量提升18%,但这又引发新的问题:光刻胶的线边缘粗糙度(LER)从2.1nm激增至3.4nm,直接导致后续蚀刻工序的缺陷率上升27%。这种“按下葫芦浮起瓢”的困境,使得7nm制程的光刻成本较10nm制程暴涨300%。

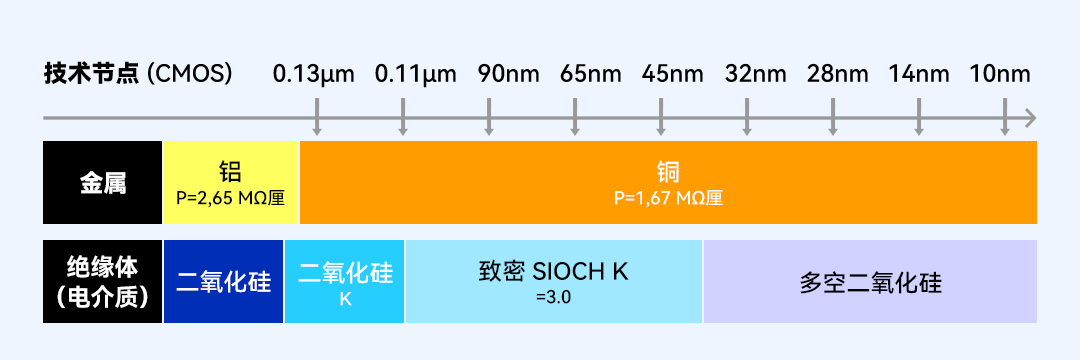

材料革命:钴互连的“阿喀琉斯之踵”

当铜互连技术在20nm制程遭遇电阻瓶颈时,钴(Co)因其更低的电阻率和更好的填充性能被寄予厚望。然而,钴互连在7nm制程中却暴露出致命缺陷:钴与硅基底的界面处易形成高电阻的硅化钴(CoSi₂),导致接触电阻较铜互连激增45%。更糟糕的是,钴的化学机械抛光(CMP)工艺会产生大量0.3-0.5μm的颗粒,这些颗粒若残留在晶圆表面,会引发局部电迁移(EM)效应,使互连线在通电后迅速形成空洞,最终导致电路断路。

英特尔的10nm+制程(相当于其他厂商的7nm)曾因钴互连缺陷导致良率暴跌至38%。其失效分析显示,在含有钴颗粒污染的晶圆上,互连线的平均寿命从设计的10年缩短至不足2年。为解决这一问题,英特尔不得不在钴互连层下方增加一层钽氮化物(TaN)阻挡层,但这又使工艺复杂度提升15%,直接推高制造成本。

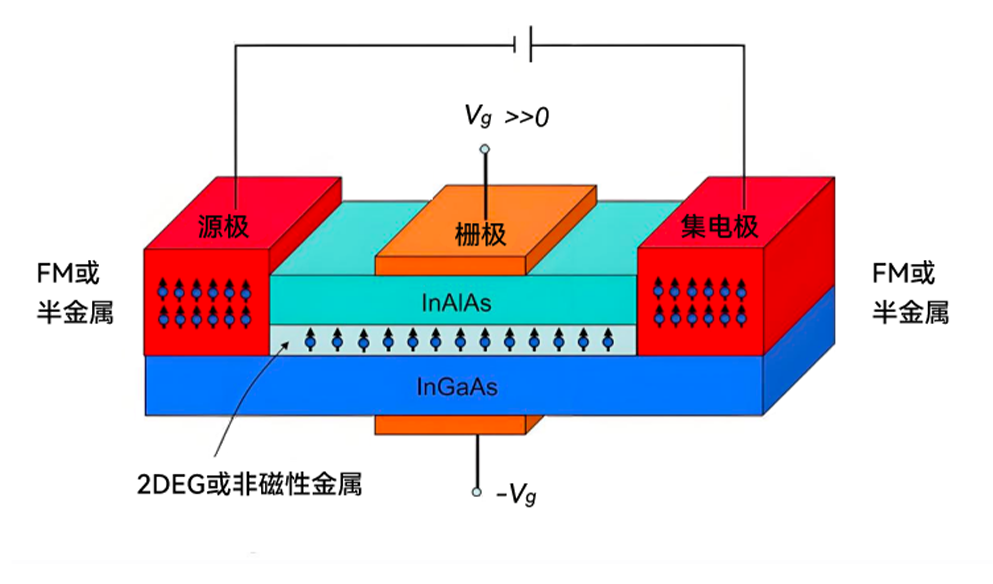

三维堆叠:FinFET的“纳米级失衡”

为应对平面晶体管的量子隧穿问题,FinFET结构在22nm制程被引入,但其三维结构在7nm制程中却成为新的缺陷源。当Fin高度从40nm增加至60nm以增强栅极控制能力时,蚀刻工艺的深宽比(AR)达到15:1,远超传统工艺的5:1。这种极端深宽比使得蚀刻气体在Fin侧壁的分布极不均匀,导致约8%的Fin出现“倾斜”或“断裂”缺陷。

三星7nm LPP工艺的扫描电镜(SEM)图像显示,在含有颗粒污染的晶圆上,Fin倾斜缺陷的发生率从正常情况的0.7%飙升至3.2%。这些倾斜的Fin会改变晶体管的阈值电压(Vth),使同一晶圆上的晶体管性能差异扩大至22%,远超设计指标的10%。为筛选出合格芯片,三星不得不将测试时间延长40%,但这仍无法完全避免缺陷芯片流入市场——2023年,某品牌旗舰手机因使用含有Fin缺陷的7nm芯片,导致部分机型出现随机重启问题,引发大规模召回。

经济黑洞:一粒灰的“百万美元代价”

在7nm制程中,一粒0.5μm颗粒引发的连锁反应,最终会转化为惊人的经济损失。

以台积电N7工艺为例:一片12英寸晶圆可切割约600颗7nm芯片,若因颗粒污染导致良率下降5%,则每片晶圆直接损失约150颗芯片。按每颗芯片售价80美元计算,单片晶圆的损失高达1.2万美元。而要维持7nm产线的运转,台积电每月需处理约10万片晶圆,这意味着颗粒污染每月可能造成超过1.2亿美元的损失。

这种经济损失正在重塑半导体行业的竞争格局。格罗方德(GlobalFoundries)因无法承受7nm制程的颗粒控制成本,于2018年宣布放弃7nm研发;联电(UMC)虽在2020年宣布突破14nm制程,却始终未敢涉足7nm领域。如今,全球仅剩台积电、三星和英特尔三家厂商仍在7nm制程上苦苦挣扎,而他们每前进一步,都要付出比前代制程高数倍的代价——这种代价,正是由“一粒灰”引发的经济黑洞。

尾言

在半导体制造的纳米级战场上,“一粒灰”已不再是简单的污染物,而是衡量人类科技极限的标尺。当工程师们用原子力显微镜(AFM)观察晶圆表面时,他们看到的不仅是光滑的硅基底,更是一场关于物理定律、材料科学和工程技术的终极博弈。在这场博弈中,每一个0.1nm的进步都需要付出数亿美元的代价,而每一次良率的提升,都是对“一粒灰”威力的重新认知。或许,只有当人类真正突破硅基半导体的物理极限时,这场由“一粒灰”引发的灾难,才能迎来终结的曙光。