前言

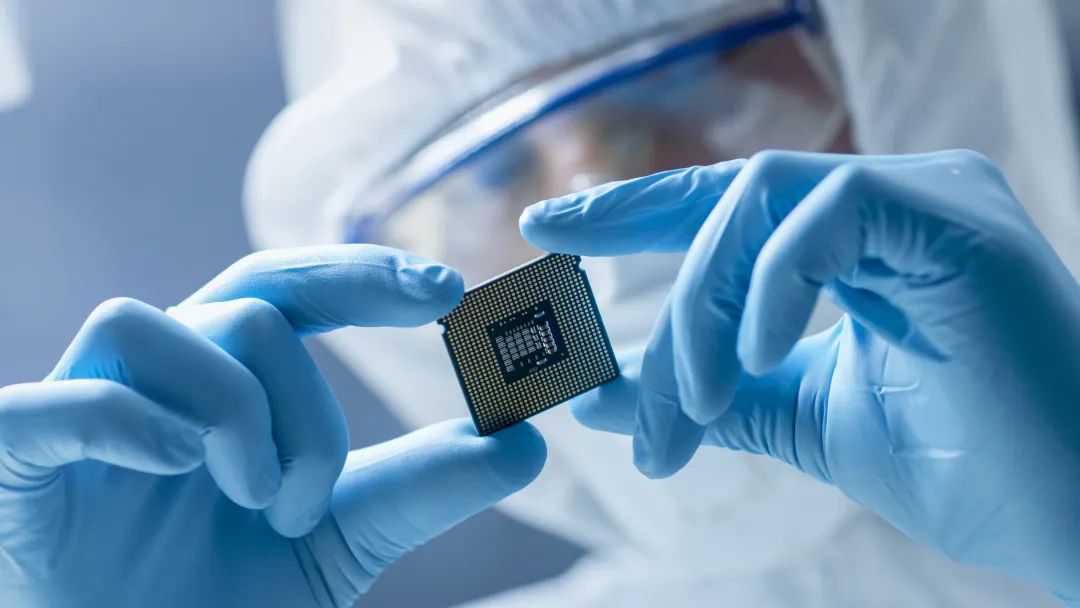

“边缘 0.15 mm 死区”并不是夸张修辞,而是 300 mm 晶圆厂光刻工程师日常面对的物理极限。从 ASML NXT:2100i 扫描式光刻机的对准系统读数看,当 overlay 预算只剩 1.4 nm 时,任何 150 µm 以内的边缘死区都会被当成“不可成像”区域直接弃用。也就是说,一片 300 mm 晶圆真正能用来放芯片的面积,被活生生削掉 7.5 mm² 的环带。听起来不多?一片 5 nm 逻辑芯片的面积约 90 mm²,等于每片晶圆白白少掉 8 颗 die。以苹果 A17 Pro 的 ASP(平均售价) 150 美元估算,一条月产 10 万片的 5 nm 线,一个月就蒸发 1.2 亿美元,一年就是 14.4 亿——这就是“每 1 µm 颗粒偷走 3 000 万美金”的算账逻辑。

真正的痛点并不在宏观面积而是在“为什么偏偏是 0.15 mm”

边缘死区 0.15mm 连锁痛点分析图表如下所示:

(1)边缘死区的物理成因:不是玄学,是电化学

在 EUV 多层膜(Mo/Si 40 层对)里,最外层 Si 的氧化层厚度必须精确到 0.7 nm。任何 1 µm 以上的微粒一旦落到晶圆边缘,后续的 CMP 会把颗粒压进氧化层,形成 5–10 nm 深的凹坑。蚀刻阶段,Cl₂ 等离子体会在凹坑底部产生局部电场增强,导致 0.15 mm 环带内的 Cu 线出现 20 % 的过蚀。过蚀会让相邻两层金属短路,良率直接掉到 0。因此,0.15 mm 不是谁拍脑袋定的,而是电化学实验里短路概率陡增的临界点。

(2)颗粒来源:不是“空气不好”,而是“材料本身在放毒”

产线里 70 % 的 1 µm 颗粒来自 FOUP(前开式晶圆传送盒)内壁脱落的 PEEK 微屑。PEEK 在 90 ℃、RH 30 % 的氮气环境里会缓慢裂解,释放 0.3–1.5 µm 的薄片。一台 AMAT Producer GT 在 6 小时内会开关 FOUP 120 次,等于把晶圆边缘当作砂纸来回擦。 再加上 ESC(静电吸盘)每次升降产生的 0.8 µm

Al₂O₃ 粉尘,边缘死区被双重夹击。

(3)检测盲区:光学散射仪看不到“透明杀手”

KLA SPOT 系列的最佳灵敏度是 80 nm SiO₂ 等效散射截面,但 PEEK 薄片在 193 nm 波长下的折射率只有 1.62,散射信号比同样体积的 SiO₂ 弱 18 dB。

结果就是:颗粒已经 1 µm,机台却报“clean”。工程师只能凭经验把边缘 0.15 mm 一刀切,宁可错杀,不敢漏检。

(4)修复技术:边缘曝光(EBR)成了“杀敌一千自损八百”

东京电子的 CLEAN TRACK ACT 12 可以在边缘 0.15 mm 做溶剂冲洗,但冲洗会把边缘的光刻胶全部剥掉,导致后续 Cu plating 时边缘没有种子层。为了补种子层,必须加一道 PVD Cu 预沉积,工艺时间增加 4 %,设备产能直接掉 3 %。一条月产 4 万片的线,3 % 的产能就是 1200 片,按每片 12 000 美元算,每月又是 1440 万美元的损失。

(5)供应链连锁反应:一颗 1 µm 颗粒,让台积电、苹果、ASML 同时背锅

当边缘死区扩大,die 的有效面积缩小,苹果就得把 A17 Pro 的 SRAM 从 32 MB 砍到 24 MB,否则芯片尺寸超标。为了维持性能,苹果只能加一颗外挂 DRAM,系统功耗上升 5 %。功耗超标又倒逼台积电把 N5 工艺再优化 0.1 V,导致 ASML 的 NXT:2100i 必须升级光源功率,从 250 W 提到 300 W,光收集器寿命缩短 20 %。最终,ASML 的维保合同每年涨价 8000 万美元,苹果每台 iPhone 15 Pro Max 的 BOM 增加 7 美元,全部源头只是一颗 1 µm 的 PEEK 薄片。

(6)终极矛盾:工艺越先进,死区越不能忍

在 2 nm 节点,overlay 预算降到 0.8 nm,边缘死区如果还是 0.15 mm,每片晶圆会损失 12 % 的 die。这意味着“颗粒控制”不再是 defectivity 问题,而是“面积经济学”问题。ASML 正在验证的下一代高 NA EUV 机台,直接把可曝光半径从 150 mm 缩到 149.85 mm,等于把 0.15 mm 死区固化到硬件里。换句话说,未来如果边缘颗粒问题不解决,新工艺节点就根本赚不到钱。

尾言

每 1 µm 颗粒偷走的 3 000 万美金,不是一次性损失,而是从 PEEK 裂解到 iPhone 涨价的整条价值链的失血。0.15 mm 边缘死区背后,是材料学、电化学、光学检测、设备产能、终端产品的连环债。只要 FOUP 里还有一片脱落的 PEEK,整个半导体产业就在为这一微米买单。