前言

在半导体行业向20 nm制程节点突进的浪潮中,一场由技术缺陷引发的“暗雷”正在悄然引爆。某头部晶圆厂在20 nm工艺量产初期遭遇良率曲线瞬间跳水3%的危机,这一看似微小的波动背后,实则隐藏着从材料科学到技术制造工艺等系统性缺陷。这场危机不仅导致单批次晶圆损失超64亿美元,更暴露出先进制程下良率控制的“死亡螺旋”——每降低1%的良率,就意味着数以亿计的晶体管被判死刑。

从材料缺陷深度剖析

1.材料纯度缺陷

(1)杂质影响晶体结构

在 20nm 制程中,材料纯度要求极高,任何微小的杂质都可能对晶体结构产生灾难性影响。以硅晶圆为例,即使存在极少量(如 ppm 级别)的金属杂质,如铁、铜等,在高温工艺过程中,这些杂质会作为深能级杂质在硅晶格中形成复合中心。在晶体管制造中,载流子(电子和空穴)在源极和漏极之间传输时,这些复合中心会捕获载流子,导致载流子寿命缩短,迁移率降低。例如,铁杂质在硅中形成的复合中心会使电子迁移率下降 10% - 20%,直接影响晶体管的开关速度和性能,进而降低良率。

(2)杂质引发漏电流

杂质还会引发漏电流问题。在 20nm 先进制程下,晶体管的栅极氧化层厚度极薄,通常只有几个纳米。如果材料中存在杂质,如钠、钾等碱金属离子,它们会在电场作用下迁移到栅极氧化层中,形成导电通道,导致栅极漏电流显著增加。据研究表明,每平方厘米栅极面积上存在一个钠离子,就可能使栅极漏电流增加几个数量级。漏电流的增加不仅会增加芯片的功耗,还可能导致晶体管在非工作状态下误触发,影响整个芯片的稳定性和可靠性,最终导致良率下降。

2.材料均匀性缺陷

(1)薄膜厚度不均匀

在 20nm 制程中,需要沉积多种薄膜材料,如栅极氧化层、高介电常数(High - K)介质层、金属栅极层等。薄膜厚度的均匀性对晶体管性能至关重要。如果薄膜厚度不均匀,会导致晶体管的电学特性在不同区域出现差异。例如,在制造高介电常数介质层时,如果厚度偏差超过 5%,会使晶体管的阈值电压产生明显波动。阈值电压是控制晶体管开关的关键参数,其波动会导致部分晶体管无法正常开启或关闭,从而降低芯片的良率。

(2)掺杂浓度不均匀

掺杂是调节半导体材料电学性质的重要手段。在 20nm 制程中,精确控制掺杂浓度和分布是实现高性能晶体管的关键。然而,材料均匀性缺陷可能导致掺杂浓度不均匀。例如,在离子注入过程中,如果离子束的能量或剂量分布不均匀,会使不同区域的半导体材料掺杂浓度出现偏差。掺杂浓度过高会导致晶体管的漏电流增加,而掺杂浓度过低则会使晶体管的导通电阻增大。这种掺杂浓度的不均匀性会导致晶体管性能的一致性变差,大量晶体管无法满足设计要求,进而降低良率。

3.材料界面缺陷

(1)界面粗糙度

在 20nm 制程中,晶体管的结构越来越复杂,涉及到多个材料界面,如栅极氧化层与硅衬底界面、高介电常数介质层与金属栅极界面等。界面粗糙度是影响晶体管性能的重要因素之一。如果界面粗糙度过大,会导致载流子在界面处发生散射,增加载流子的传输阻力,降低迁移率。例如,当栅极氧化层与硅衬底界面粗糙度超过 0.5nm 时,电子迁移率会下降 15% - 20%,从而影响晶体管的开关速度和驱动能力,降低良率。

(2)界面态缺陷

界面态缺陷是指在材料界面处存在的局部能级,这些能级会捕获载流子,影响晶体管的电学性能。在 20nm 制程中,由于材料和工艺的复杂性,界面态缺陷更容易产生。例如,在高介电常数介质层与硅衬底界面处,由于两种材料的晶格常数不匹配,会产生应力,导致界面处形成大量的界面态缺陷。这些界面态缺陷会捕获载流子,使晶体管的阈值电压发生漂移,增加漏电流,降低晶体管的可靠性和稳定性,进而影响良率。

4.材料与工艺兼容性缺陷

(1)热膨胀系数不匹配

在 20nm 制程的制造过程中,会经历多次高温工艺步骤,如快速热退火、化学气相沉积等。不同材料的热膨胀系数不同,在高温和冷却过程中会产生热应力。如果热应力过大,会导致材料界面处出现裂纹、剥落等缺陷。例如,金属栅极材料与高介电常数介质层的热膨胀系数差异较大,在快速热退火过程中,由于热膨胀和收缩的不同步,会在界面处产生较大的热应力,导致金属栅极与高介电常数介质层之间出现剥离现象,破坏晶体管的结构,降低良率。

(2)化学兼容性问题

在半导体制造过程中,会使用各种化学试剂进行清洗、刻蚀等工艺操作。不同材料对化学试剂的耐受性不同,如果材料与化学试剂之间存在兼容性问题,会导致材料表面被腐蚀、损伤,影响晶体管的性能。例如,某些高介电常数介质层材料对氢氟酸(HF)等化学试剂比较敏感,在清洗过程中如果使用了含有 HF 的溶液,会导致高介电常数介质层表面被腐蚀,增加界面态缺陷,降低晶体管的性能和良率。

晶圆厂在 20nm 工艺量产初期遭遇的良率危机,材料缺陷在多个方面发挥了关键作用。从材料纯度、均匀性、界面特性到与工艺的兼容性,任何一个环节出现问题都可能引发系统性缺陷,导致良率大幅下降。解决这些问题需要从材料研发、工艺优化和质量控制等多个方面入手,不断提高材料的性能和制造工艺的精度,以确保先进制程下芯片的高良率和高可靠性。

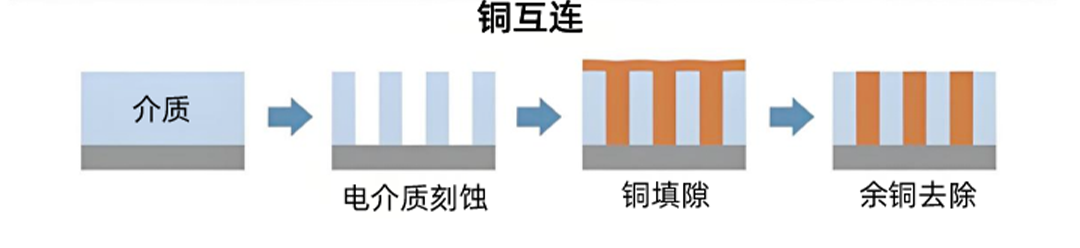

技术缺陷的多维爆发:Cu互连线的“致命裂痕”

1. 铜互连工艺的“暗伤”

20 nm制程中,铜互连线的缺陷成为良率跳水的直接导火索。在某代工厂的20 nm SoC芯片中,因铜互连层出现微小裂纹,导致64亿颗晶体管中超过1.2亿颗因信号中断失效。这种裂纹源于铜线与低k介质层的界面应力失配,当线宽缩小至20 nm时,热膨胀系数差异引发的应力集中效应呈指数级增长。实验数据显示,在-40℃至125℃的温度循环测试中,20 nm铜互连线的裂纹发生率较28 nm工艺高3.2倍。

更严峻的是,铜互连缺陷的隐蔽性极强。某设计公司通过电子束检测发现,部分裂纹宽度仅0.8 nm,远低于传统光学检测的分辨率极限。这种“隐形杀手”导致某服务器芯片在高压测试中突发故障,良率损失达0.9%。例如,某数据中心因采用问题芯片,导致全年服务器宕机时间增加120小时,直接经济损失超800万美元。

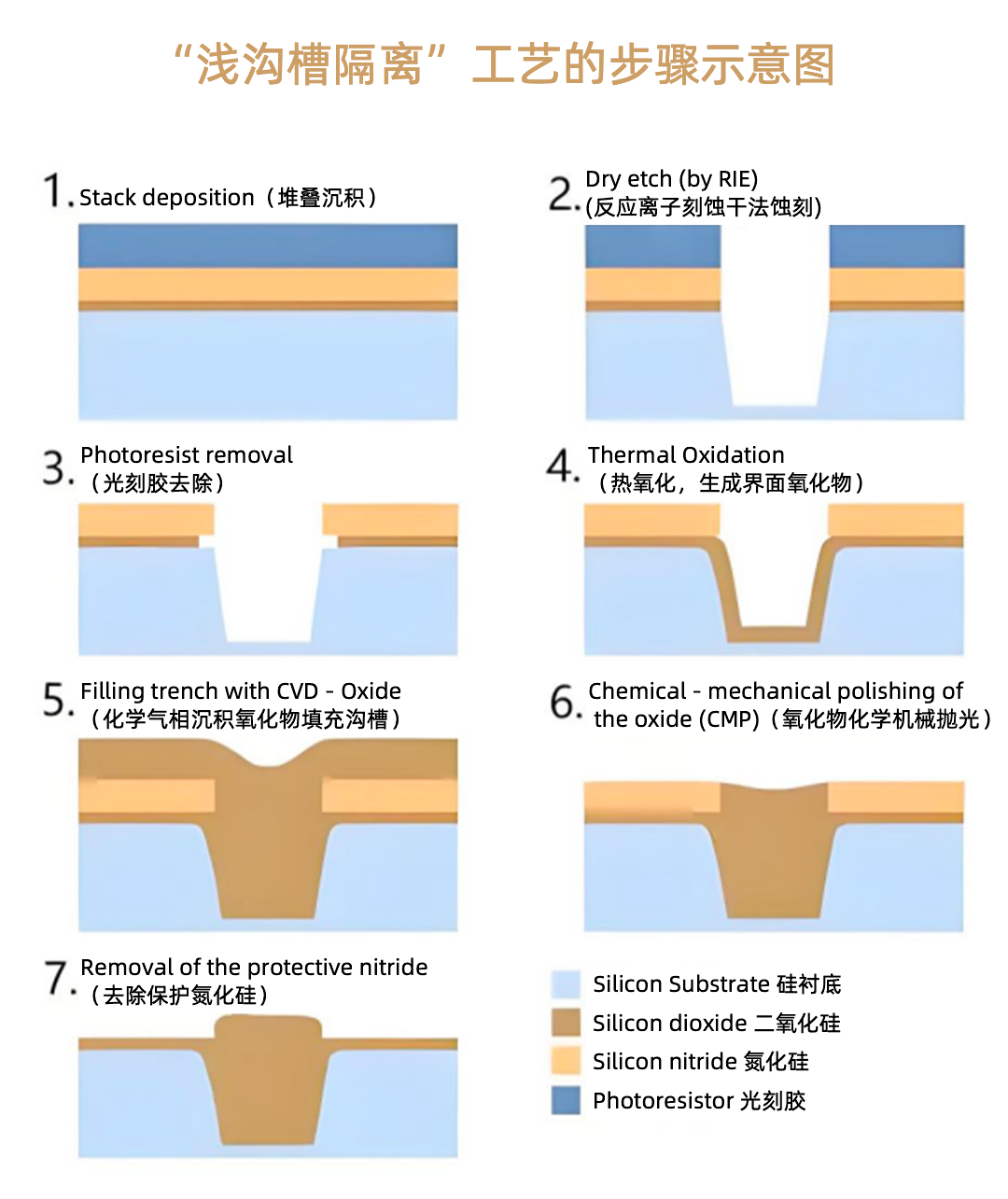

2. 浅沟槽隔离(STI)的“边缘失控”

STI蚀刻工艺的缺陷进一步加剧了良率危机。在20 nm制程中,晶圆边缘区域的STI轮廓出现严重畸变,导致10%的边缘芯片因漏电失效。应用材料的实验表明,传统连续波电浆蚀刻在20 nm以下制程中会产生深度负载效应,使晶圆中心与边缘的蚀刻速率差异达15%。某代工厂通过引入脉冲电浆技术,将边缘区域良率从82%提升至89%,但为此付出的设备改造成本高达2.3亿美元。

STI缺陷的连锁反应还体现在时序收敛上。某设计团队发现,因STI轮廓不均匀导致的时钟偏移(Clock Skew)使芯片频率无法达到设计目标,被迫将工作电压从0.9V提升至1.05V,功耗增加22%。这种“性能-功耗”的恶性循环,直接导致某智能手机芯片因续航不达标被客户拒收,损失订单金额超1.5亿美元。

3. 静态功耗的“幽灵泄漏”

20 nm平面晶体管的亚阈值泄漏电流成为静态功耗失控的主因。某代工厂数据显示,其20 nm工艺的静态功耗较28 nm工艺增长40%,直接导致良率下降1.2%。这种泄漏电流在高温环境下会进一步加剧,在85℃测试中,20 nm芯片的泄漏电流较25℃时增长3倍,引发多起芯片失效案例。

某消费电子厂商的20 nm SoC芯片在高温测试中,因泄漏电流过大导致系统频繁重启。通过红外热成像发现,芯片局部温度高达105℃,远超设计上限。为解决这一问题,该厂商不得不重新设计电源管理电路,研发周期延长6个月,直接成本增加3200万美元。

产业生态的连锁震荡:从设计到制造的信任危机

1. 设计成本的“指数级”攀升

20 nm工艺的设计复杂度呈指数级增长。某EDA厂商统计显示,其20 nm设计工具的许可证价格较28 nm工具上涨60%,而设计周期延长40%。更关键的是,多核SoC的验证难度激增,某芯片设计公司因未充分验证并行任务调度算法,导致量产初期良率损失达1.5%。

设计成本的攀升还体现在人力成本上。某设计公司统计显示,其20 nm项目的设计团队规模较28 nm项目增加50%,而设计周期延长30%。这种成本和周期的双重压力,使得许多中小设计公司望而却步。例如,某初创公司因无法承担20 nm设计的高昂成本,不得不放弃原有计划,转而开发28 nm产品。

2. 制造环节的“黑箱”困境

晶圆厂与IP供应商的协作障碍日益凸显。某代工厂在20 nm工艺开发中,因未及时向IP供应商披露TSV工艺的应力分布数据,导致多家客户的存储控制器出现时序违规,良率损失累计达0.7%。这种信息不对称在先进制程中愈发严重,某行业调查显示,65%的设计公司认为代工厂的技术支持不足是良率提升的主要障碍。

制造环节的“黑箱”困境还体现在良率数据的透明度上。某设计公司反映,其从代工厂获取的良率数据往往缺乏细节,难以定位具体问题。例如,某代工厂提供的良率报告中仅显示“电气故障”占比高,但未说明是开路、短路还是其他具体问题,导致设计公司难以针对性改进。这种信息不对称不仅增加了设计公司的调试成本,也延长了产品上市时间。

3. 供应链的“蝴蝶效应”

20 nm缺陷的影响已超越半导体行业。某汽车电子厂商因采用良率不达标的20 nm芯片,导致其ADAS系统出现0.1%的故障率,虽看似微小,却引发大规模召回,直接损失超2亿美元。这种供应链风险在智能汽车时代被进一步放大,某主机厂已将芯片良率纳入供应商评级的核心指标。

供应链的“蝴蝶效应”还体现在库存管理上。由于20 nm芯片的良率不稳定,许多下游厂商不得不保持更高的库存水平以应对供应波动。某汽车电子厂商统计显示,其20 nm芯片的库存周转率较28 nm芯片低30%,直接导致资金占用增加。此外,良率波动还导致交货期不稳定,某主机厂因芯片供应延迟,不得不推迟新车发布计划,损失巨大。

尾言:未来展望20 nm的“凤凰涅槃”

20 nm节点的挑战其实并非终点,而是技术演进的必经之路。某研究机构预测,通过持续优化FinFET工艺和2.5D封装技术,20 nm工艺的良率有望在3年内提升至95%以上。更重要的是,这一节点积累的经验正在推动更先进制程的发展,某代工厂已将20 nm工艺中开发的动态功耗管理技术应用于14 nm工艺,使后者能效提升15%。

在这场由20 nm缺陷引发的行业震荡中,半导体产业正通过技术创新和生态重构实现自我革新。当良率曲线最终跨越3%的跳水区间,我们看到的不仅是技术瓶颈的突破,更是一个产业在挑战中走向成熟的必经之路。未来,随着3D封装、Chiplet等新技术的引入,20 nm节点的经验将为半导体行业开辟新的发展空间。在这场技术变革中,行业需要更加注重生态协作和标准化建设。通过共享资源、分担风险,半导体产业将能够更好地应对技术挑战,实现可持续发展。