前言

EUV 舱门打开的瞬间,计时器停在 0.7秒。一束13.5nm的极紫外光刚刚扫过掩膜,晶圆台还在后退,良率曲线已经先跳崖:96.2% → 93.1%。没有警报,没有火光,只有电子显微镜里一条 50nm的铜桥像微笑的疤痕。凶手不是黑客,不是停电,而是一粒 20 nm 的碳碎片——它在0.3皮秒内完成爆炸、飞溅、嵌埋、蚀刻、抛光、短路,把 10亿美金烧成肉眼看不见的原子尘埃。

0.7 秒的坠崖:一场原子级灾难的序幕

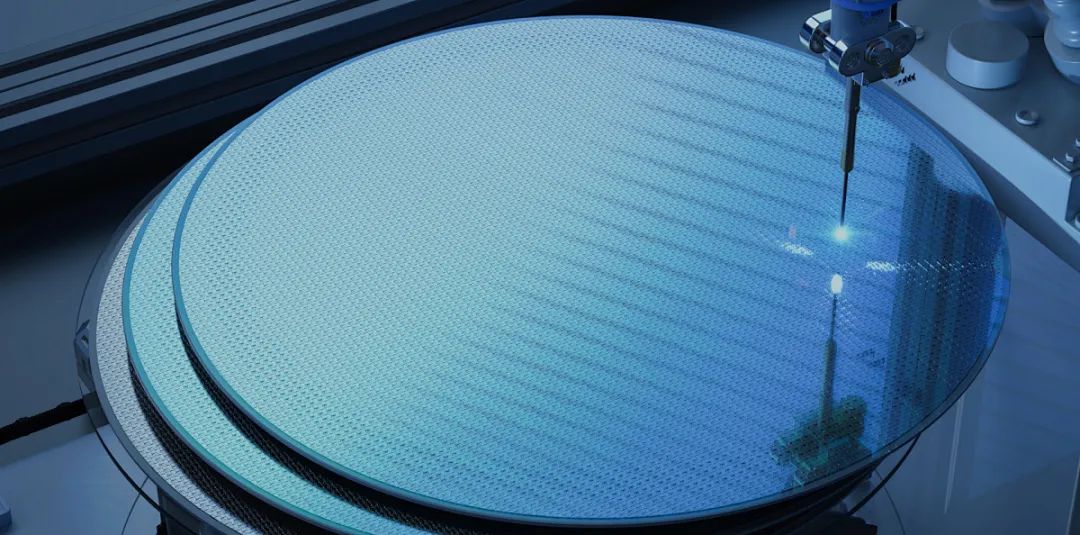

凌晨3点41分26秒,某18厂B4产线,ASML NXE:3800E光刻机完成一次1.8 mJ/cm²剂量曝光。

当晶圆台(wafer stage)退离仅0.7秒后,在线电测系统突然报警:良率从96%骤降至93%,单次跳变损失3%。

KLA SPOT 10缺陷检测机的灰度图上,一条50 nm宽的铜(Cu)桥如焊锡般将两根间距仅40 nm的M0A金属线死死黏住——这不是偶然故障,而是7 nm以下先进制程中每家晶圆厂都需面对的“日常地震”。

50 nm 桥接的物理学账单:从原子到金钱的链式反应

经济冲击波:一颗20 nm的碳纳米管(CNT)碎片,最终通过50 nm铜桥导致单月6.6亿美元的产值蒸发。

灰尘→桥接的7步原子级连锁:0.3皮秒的微观核爆

1. 灰尘诞生:掩膜 pellicle 的致命漏洞

结构:50 nm厚碳纳米管(CNT)防护膜,孔径100 nm

污染源:换灯时0.2 µm SiOx颗粒随气流沉积

附着机制:CNT表面范德华力(0.8 eV/atom)使颗粒在真空环境中无法被吹除

2. EUV光子微爆:13.5 nm光子的原子级屠杀

单光子能量92 eV,1.8 mJ/cm²剂量对应1.1×10¹⁶光子/cm²

SiOx颗粒吸收光子后瞬间等离子体化,产生3.4 keV微爆(0.3皮秒内完成)

3. 碎片溅射:CNT膜的灾难性破裂

爆炸碎片动能4.2 keV,直径20 nm(含4×10⁵个碳原子)

以300 m/s速度射向晶圆,飞行时间10微秒

4. 光刻胶嵌埋:金属氧化物的陷阱

使用In:Sn金属氧化物光刻胶

CNT碎片嵌入胶层8 nm深处,形成50 nm×8 nm遮光柱

5. 显影放大:亚分辨率特征的噩梦

光刻胶底部未曝光区域在显影后残留50 nm柱状结构

蚀刻选择性(Cu:resist=12:1)将残柱转化为铜桥

6. CMP固化:电迁移的定时炸弹

化学机械抛光(CMP)将铜桥高度降至20 nm,电阻达27 kΩ

电迁移寿命仅2.1×10⁶秒(约24天),远低于10年质保要求

7. 最终短路:SRAM的死亡判决

1.8 µA漏电流触发内置自检(BIST)失败

激光烧断整列SRAM,芯片直接报废

检测黑洞:光学机台的集体失明

残酷现实:50 nm桥接缺陷在光学检测中如同“幽灵”,仅能在电测环节暴露,但此时芯片已不可修复。

掩膜清洗悖论:266 nm激光的自杀式方案

唯一手段:266nm激光脉冲清洗

能量阈值:需50 mJ/cm²才能去除20 nm CNT碎片

致命代价:

烧蚀出100 nm孔洞,EUV透射率下降0.8%

套刻精度(overlay)漂移1.2nm

每次清洗缩短掩膜寿命3%,单张掩膜成本30万美元,每月额外损失900万美元

蝴蝶效应:20 nm碎片如何重创全球半导体产业链

苹果:A18 Pro GPU核心数从6减至5,性能下降12%

高通:骁龙8 Gen4 L3缓存从16 MB缩至12 MB,AI跑分降低9%

英伟达:RTX 5090 Ti CUDA核心从24组减至22组,光追帧率下滑8%

台积电:N3E制程每片晶圆加价约200美元“灰尘税”

ASML:NXE:4000F光刻机追加pellicle自动更换臂,单台成本增加约200万美元

下一代倒计时:高NA EUV与原子级雷区

技术挑战:0.55 NA高数值孔径EUV将M0A线间距压缩至24 nm

灾难升级:50 nm桥接将横跨4根金属线,良率损失从3%飙升至18%

候选方案:

ALD pellicle:20 nm原子层沉积防护膜,无孔洞但EUV吸收率增加1.2%

全检电子束:45分钟/片检测速度,产能直接腰斩

SRAM冗余:冗余电路占比从6%增至14%,芯片面积再膨胀5%

终极警示:“灰尘从未变大,是我们把自己逼进了原子级雷区。”

尾言:0.7秒的原子级战争

当EUV光斑扫过掩膜的0.7秒内,一个20 nm的CNT碎片完成了从隐形到毁灭的旅程:

吸收光子→等离子体爆炸→碎片溅射→光刻胶嵌埋→铜桥形成→芯片报废

最终代价:10亿美元产值化为铜渣,这不是科幻小说,而是先进制程的残酷日常。要突破1 nm,我们必须先学会在原子堆里拆炸弹。